# Design and Implementation of a FIR Digital Band Pass Filter (BPF) using FPGA

# Dr. Kamal Aboutabikh 1, Dr. Maarouf Yousef 2

Faculty of Informatics Engineering, Ittihad Private University, Damascus- Syria<sup>1</sup>

Electrical Engineering faculty, Aleppo University, Syria<sup>2</sup>

#### **Abstract:**

Digital signal filtering is used in many different fields, including communications, radar, navigation and others, because of its excellent performance and the ability to obtain accurate results using FIR and IIR filters.

In this paper, we propose the design and implementation mechanism for FIR digital BPF based on the use of Cyclone II EP2C20F484C7 FPGA from ALTERA, placed on education and development board DE-1. The designed filter has the following parameters:

- -Clock frequency: F<sub>CLK</sub>=50 MHz.

- -Sampling frequency: fsam= 2 MHz.

- -Cut- off frequency of the band pass filter (BPF): fcut1=100 KHz, fcut2=200 KHz.

- -Type of input signal is: sinusoidal of frequency: finp1=95 KHz, finp2=97 KHz, finp3=100 KHz, finp4=150 KHz, finp5=200 KHz, finp6=203 KHz, finp7=203 KHz,

- -The ROM capacity for the stored input signal samples is 8192X8 bits, and their values are positive within the range from

(0 to 255).

- -Frequency range: (0.0001 Hz...1 MHz).

- -Frequency Resolution: (0.0001 Hz).

- Signal amplitude (5V).

Digital designs using FPGA allow the system to be modified and developed to obtain better results through reprogramming according to the user's desire.

**Keywords:** digital filter, FIR, BPF, DDFS, FPGA.

# I. INTRODUCTION

FPGA is considered as one of the distinctive tools for designing digital filters, because it contains a large number of logical elements. It is possible to design digital filters with a high order. Multi-shape windows can also be used to improve specifications of digital filter.

In this paper, we propose a new method to replace floating-point coefficients with integer coefficients, which makes the filtering process parallel and fast, and reduces the memory capacity used to store the coefficients, and approaches the accuracy of the fractional coefficient case.

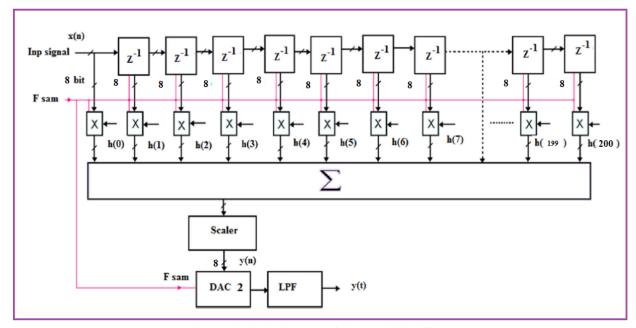

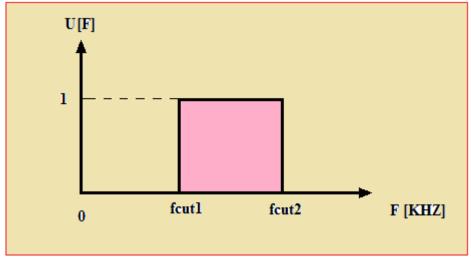

The coefficients of the designed FIR digital BPF h(n) are computed in (MATLAB) environment, and converted to signed values (-127,...,+127) with length (8) bits, then they are used in the filter design program by (VHDL) language, where the digital convolution algorithm of the FIR digital BPF is implemented for impulse response samples of length (N=201) as shown in figure (1), where( $Z^{-1}$ ) represents a digital delay line of length (8) bits and a delay time equal to sampling pluses period (Tsam=0.5usec). This digital BPF is designed by (VHDL) [1] with (Quartus II9.1) programming environment according to the ideal frequency response shown figure (2).

reference [2] presents the Design and Implementation of Low-Pass, High-Pass and Band-Pass Finite Impulse Response (FIR) Filters Using FPGA, where filter order is 91, and filter band 30 KHz.

Fig. 1: The block diagram of the FIR digital filter

Fig. 2: The ideal frequency response of the digital BPF

#### II. RESERCH IMPORTANCE AND ITS OBJECTIVES

- -In this paper, FIR digital BPF was designed, implemented and tested based on the use of FPGA, VHDL and Graphical programming language of Quartus II 9.1 design environment.

- -Using the digital convolution with mathematical operations (shifting, adding, multiply, division), makes the digital filters design process flexible, accurate and highly efficient.

- -Changing the parameters of input signal (frequency), windows type, and filters order explains the difference between digital filters and analog filters.

#### III. RESERCH MATERIALS AND ITS WAYS

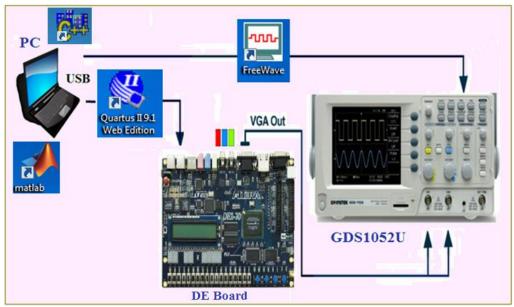

The following tools and software are used to design, and test digital filters of different types (LPF, HPF, BPF), different window types, and different values of input signals:

- -Cyclone II EP2C20F484C7 FPGA chip from ALTERA with highly accuracy, speed, and level specifications, placed on education and development board DE-1 [3].

- -DDFS which is considered as highly accuracy techniques in sinusoidal and square signals synthesizing on FPGA chips.

- -VHDL programming language with Quartus II 9.1 design environment.

- -Design Environment MATLAB.

- -GDS-1052 digital oscilloscope with Free Wave program to take the results.

- -PC computer for designing and injecting the design in the FPGA chip.

The block diagram of the laboratory experiment platform [4] is shown in figure (3).

Fig (3): Block diagram of the laboratory experiment platform

# IV. FILTERING ALGORITHM

The FIR digital filter output signal can be represented according to the following convolution relationship [5]:

$$y(n) = h(n) * x(n) = \sum_{k=0}^{N-1} h(k) . x(n-k)$$

(1)

Where: x(n) is the input signal samples in digital form.

*N* is number of samples for impulse response of the filter.

*n* is the sample number for input and output signals.

h(n) is the impulse response samples for digital filter, and it is given to BPF according to the following relationship [6]:

$$a_0 = h(0) = 2 \frac{f_{cut2-fcut1}}{f_{sam}}$$

, for  $k = 0$  (2)

$$a_k = h(k) = \frac{1}{\pi k} \left\{ \sin \left( 2\pi k \frac{f_{cut2}}{f_{sam}} - 2\pi k \frac{f_{cut1}}{f_{sam}} \right) \right\} , \quad for \ k \neq 0$$

(3)

Where:

$$n = 0, \ldots, N-1$$

$$-\frac{(N-1)}{2} \le k \le \frac{(N-1)}{2} \tag{4}$$

For N=201:

$$-\frac{(N-1)}{2} \le k \le \frac{(N-1)}{2} \Rightarrow -100 \le k \le -100$$

A Peer-reviewed journal Volume 2, Issue 3, March 2025 DOI 10.17148/IMRJR.2025.020311

$$h_{nor}(k) = \frac{h(k)}{h_{MAX}(k)} \tag{5}$$

$$h_{int}(k) = INT[127 * h_{nor}(k)]$$

(6)

# Where:

$h_{nor}(k)$  Relative value,  $h_{MAX}(k) = 0.9$  Maximum value,  $h_{int}(k)$  Integer value.

The values of h(k) are calculated using the MATLAB environment ,Toolboxes-Filter Design-Filter Design & Analysis Tool (fdatool) , and then  $h_{nor}(k)$  ,  $h_{MAX}(k)$  ,  $h_{int}(k)$  are recalculated according to the relationships (5) ,(6) and recorded in table (1).

| Table (1)                               |    |        |        |        |        |       |       |       |         |  |

|-----------------------------------------|----|--------|--------|--------|--------|-------|-------|-------|---------|--|

| n                                       | 0  | 1      | 2      | 3      | 4      | 5     | 6     | 7     | 8       |  |

| k=n-100                                 | -  | -99    | -98    | -97    | -96    | -95   | -94   | -93   | -92     |  |

|                                         | 10 |        |        |        |        |       |       |       |         |  |

|                                         | 0  |        |        |        |        |       |       |       |         |  |

| h(k)                                    | 0  | -      | 0.0011 | -      | 0.0012 | 0.003 | 0.005 | 0.006 | 0.00532 |  |

|                                         |    | 0.0008 | -799   | 0.0004 | 05     | 351   | 211   | 024   | 4       |  |

|                                         |    | 96     |        | 66     |        |       |       |       |         |  |

| $\mathbf{h}_{\text{nor}}(\mathbf{k}) =$ | 0  | -      | 0.0117 | -      | 0.0120 | 0.033 | 0.052 | 0.060 | 0.06024 |  |

| $h(k)/h_{max}(k)$                       |    | 0.0089 | -99    | 0.0046 | 5      | 51    | 11    | 24    |         |  |

|                                         |    | 6      |        | 6      |        |       |       |       |         |  |

| h <sub>int</sub> (k)=                   | 0  | -1     | -2     | -1     | 2      | 4     | 7     | 8     | 7       |  |

| INT[127* hnor                           |    |        |        |        |        |       |       |       |         |  |

| (k)]                                    |    |        |        |        |        |       |       |       |         |  |

| n                                         | 92    | 93    | 94      | 95      | 96      | 97      | 98      | 99      | 100 |  |

|-------------------------------------------|-------|-------|---------|---------|---------|---------|---------|---------|-----|--|

| k=n-100                                   | -8    | -7    | -6      | -5      | -4      | -3      | -2      | -1      | 0   |  |

| h(k)                                      | -     | -     | -       | -       | -       | 0.01507 | 0.05781 | 0.08873 | 0.1 |  |

|                                           | 0.061 | 0.080 | 0.08163 | 0.06366 | 0.02890 | 09      | 6       | 4       |     |  |

|                                           | 285   | 036   | 8       | 2       | 8       |         |         |         |     |  |

| $\mathbf{h}_{\mathbf{nor}}(\mathbf{k}) =$ | -     | -     | -       | -       | -       | 0.15070 | 0.57816 | 0.88734 | 1   |  |

| h(k)/                                     | 0.612 | 0.800 | 0.81638 | 0.63662 | 0.28908 | 9       |         |         |     |  |

| h <sub>max</sub> (k)                      | 85    | 36    |         |         |         |         |         |         |     |  |

| h <sub>int</sub> (k)=                     | -78   | -102  | -104    | -81     | -37     | 19      | 73      | 113     | 127 |  |

| INT[127*                                  |       |       |         |         |         |         |         |         |     |  |

| h <sub>nor</sub> (k)]                     |       |       |         |         |         |         |         |         |     |  |

| n                      | 192   | 193     | 194     | 195   | 196      | 197   | 198   | 199     | 200 |  |

|------------------------|-------|---------|---------|-------|----------|-------|-------|---------|-----|--|

| k=n-100                | 92    | 93      | 94      | 95    | 96       | 97    | 08    | 99      | 100 |  |

| h(k)                   | 0.005 | 0.00602 | 0.00521 | 0.003 | 0.001205 | -     | -     | -       | 0   |  |

|                        | 324   | 4       | 1       | 351   |          | 0.000 | 0.001 | 0.00089 |     |  |

|                        |       |         |         |       |          | 466   | 180   | 6       |     |  |

| h <sub>nor</sub> (k) = | 0.053 | 0.06024 | 0.05211 | 0.033 | 0.001205 | -     | -     | -       | 0   |  |

| $h(k)/h_{max}(k)$      | 24    |         |         | 51    |          | 0.004 | 0.011 | 0.00896 |     |  |

|                        |       |         |         |       |          | 66    | 80    |         |     |  |

| h <sub>int</sub> (k)=  | 7     | 8       | 7       | 4     | 2        | -1    | -2    | -1      | 0   |  |

| INT[127*               |       |         |         |       |          |       |       |         |     |  |

| h <sub>nor</sub> (k)]  |       |         |         |       |          |       |       |         |     |  |

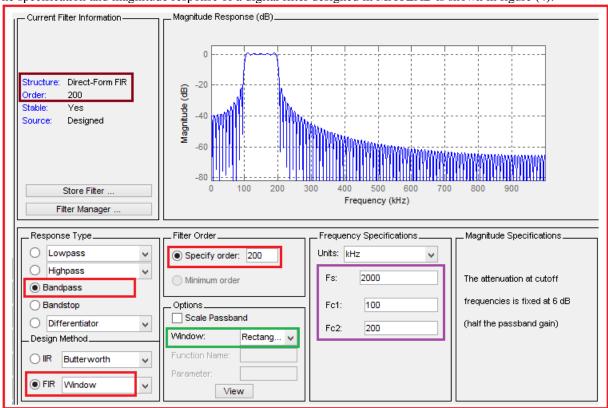

# V. DESIGN OF THE DIGITAL FILTER USING MATLAB

The FIR digital band pass filter (BPF) was designed using MATLAB and VHDL with the following parameters [7]:

-Type of filter: BPF.

- Filter structure: Direct form - FIR

-Filter order: 200. -Filter length: 201.

-Sampling frequency: 2MHz.

A Peer-reviewed journal Volume 2, Issue 3, March 2025 DOI 10.17148/IMRJR.2025.020311

- -Frequencies of input signals: finp1=95 KHz, finp2=97 KHz, finp3=100 KHz, finp4=150 KHz, finp5=200 KHz, finp6=203 KHz, finp7=205 KHz.

- -Cut-off frequency of BPF: fcut1=100 KHz, fcut2=200 KHz.

- -Window type: Rectangular.

- -Word length: 8 bits.

The specification and magnitude response of a digital filter designed in MATLAB is shown in figure (4).

Fig (4): The specification and magnitude response of a digital filter designed in MATLAB

# VI. DESIGN OF THE DDFS USIGN QUARTUS II 9.1

The designed DDFS has the following parameters:

- -The frequency step i :  $\delta f = 0.0001 \, Hz$  , and  $f_{sam} = 2 \, MHz$  .

- -The input signal is sinusoidal of frequency finp1=95 KHz, finp2=97, finp3=100 KHz, finp4=150 KHz , finp5=200 KHz , finp6=203 KHz, finp7=205 KHz, and fsam= 2 MHz.

- -The ROM capacity for the stored signal samples 8192X8 bits, and their values are positive within the range from 0 to 255.

- -The number of the accumulator bits is computed from the following mathematical relation [8]:

$$\delta f = \frac{f_{sam}}{2^n}$$

$$\delta f = \frac{f_{sam}}{2^n} \Longrightarrow 2^n = \frac{f_{sam}}{2^n} = \frac{2 \times 10^6}{0.0001} \Longrightarrow n = 32 \text{ bits}$$

(7)

-The frequency range for the DDFS is computed from the following mathematical relation:

$$\Delta f = 0 \dots \frac{f_{sam}}{2} = 0 \dots 1 MHz$$

- The frequency code is calculated according the following relation [9]:

$$Code f = L = \frac{f \cdot 2^{n}}{f_{sam}}$$

(8)

So to synthesize seven input signals of frequencies  $f_{inp1}=95~\rm KHz$ ,  $f_{inp2}=97~\rm KHz$ , finp3=100 KHz, finp4=150 KHz, , finp5=200 KHz, finp6=203 KHz, finp7=205 KHz and fsam= 2 MHz, the frequency code of each one will be:

Code

$$f_{sam} = L_{sam} = \frac{f \cdot 2^{n}}{F_{CLK}} = \frac{2X \cdot 2^{32}}{50} = 171798692$$

Code

$$f_{inp1} = L_{inp1} = \frac{f_{inp1} \cdot 2^{n}}{f_{sam}} = \frac{0.095X \ 2^{32}}{2} = 204010946$$

Code

$$f_{inp2} = L_{inp2} = \frac{f_{inp2} \cdot 2^{n}}{f_{sam}} = \frac{0.097X \cdot 2^{32}}{2} = 208305914$$

Code

$$f_{inp3} = L_{inp3} = \frac{f_{inp3} \cdot 2^{n}}{f_{sam}} = \frac{0.100X \ 2^{32}}{2} = 2147483648$$

Code

$$f_{inp4} = L_{inp4} = \frac{f_{inp4} \cdot 2^{n}}{f_{sam}} = \frac{0.150X \ 2^{32}}{2} = 322122547$$

Code

$$f_{ip5} = L_{inp5} = \frac{f_{inp5} \cdot 2^{n}}{f_{sam}} = \frac{0.200X \ 2^{32}}{2} = 429496730$$

Code

$$f_{ip6} = L_{inp6} = \frac{f_{inp6} \cdot 2^{\text{n}}}{f_{sam}} = \frac{0.203 X \ 2^{32}}{2} = 435939181$$

Code

$$f_{ip7} = L_{inp7} = \frac{f_{inp7} \cdot 2^{n}}{f_{sam}} = \frac{0.205X \cdot 2^{32}}{2} = 440234148$$

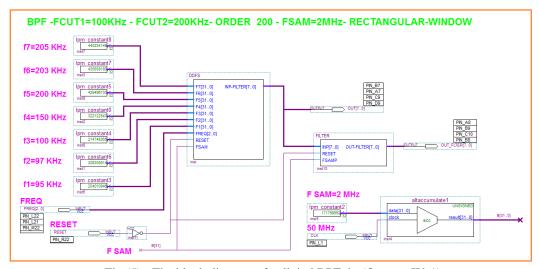

The block diagram of the digital BPF designed in (Quartus II9.1) environment is shown in figure (5).

Fig (5): The block diagram of a digital BPF in (Quartus II9.1)

A Peer-reviewed journal Volume 2, Issue 3, March 2025 DOI 10.17148/IMRJR.2025.020311

#### VII. RESULTS OF DESIGN

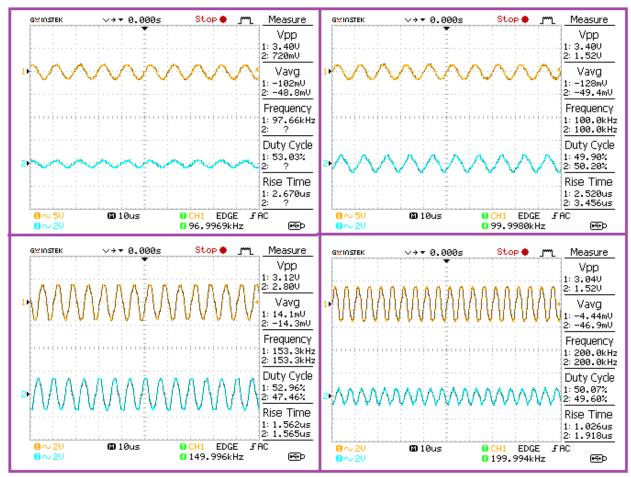

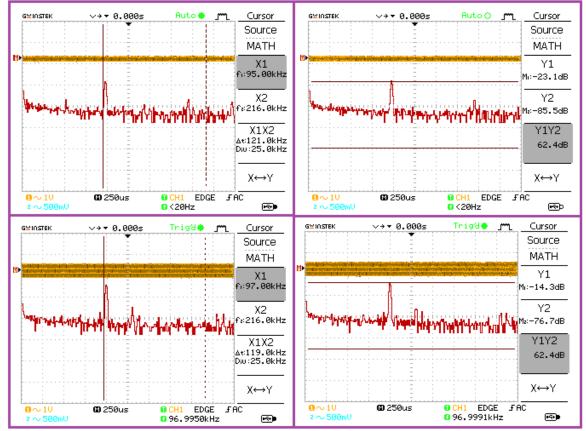

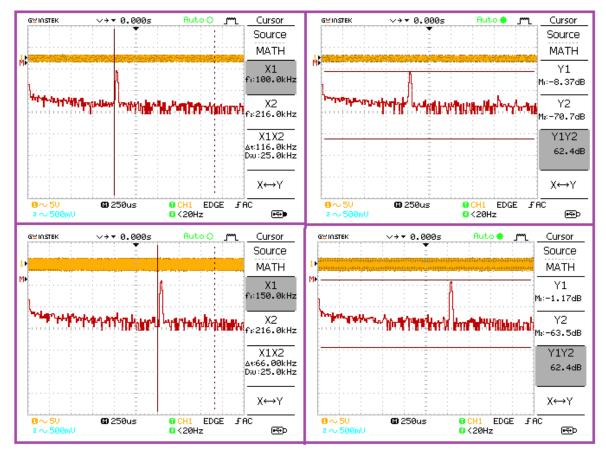

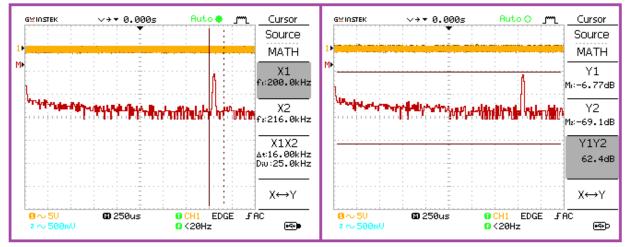

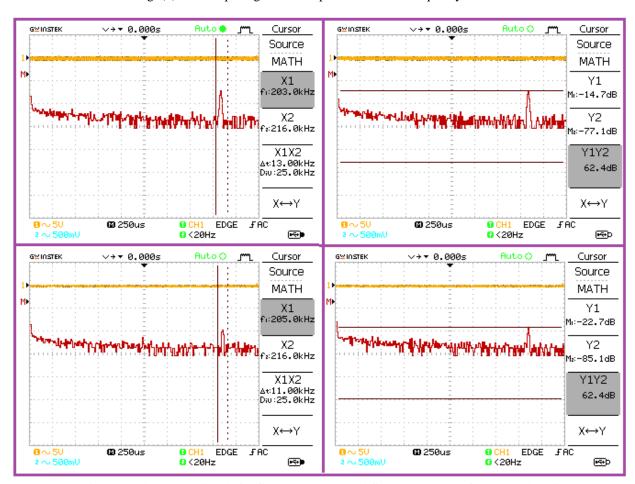

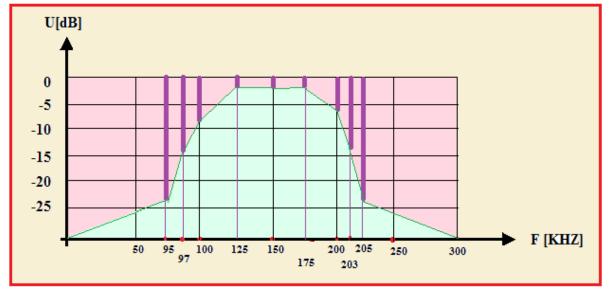

The results of the practical design of the digital BPF for different cases (finp2=97 KHz, finp3=100 KHz, finp4=150 KHz, finp5=200 KHz) in time domain are shown in figure. (6). The results of the practical design of the digital BPF for the same previous cases in frequency domain are shown in figure (7), figure (8), figure (9) and figure (10). These figures are taken from the screen of digital oscilloscope, and digital spectrum analyzer. We notice from these figures the identification between the theoretical results and the practical results, which indicate the high accuracy of digital synthesizing and filtering operations.

Fig. (6): The input and output signals of BPF for finp2=97 KHz, and finp3 = 100 KHz, finp4=150 KHz and finp5=200 KHz in time domain.

Fig. (7): The output signals for finp1=95 and finp2=97 KHz in frequency domain.

Fig. (8): The output signals for finp3=100 KHz and finp4=150 KHz in frequency domain

Fig. (9): The output signals for finp5=200 KHz in frequency domain

Fig. (10): The output signals for finp6=203 KHz and finp7=205 KHz frequency domain

The values [Uout] for different input frequencies are recorded in table (2).

| Table (2).                                                        |       |       |       |       |       |       |       |       |       |  |

|-------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| Values [Uout] For Deference Frequency                             |       |       |       |       |       |       |       |       |       |  |

| f                                                                 | 95    | 97    | 100   | 125   | 150   | 175   | 200   | 203   | 205   |  |

| inp[KHZ]                                                          |       |       |       |       |       |       |       |       |       |  |

| Uout [dB]                                                         | -23.1 | -14.3 | -8.37 | -1.18 | -1.17 | -1.17 | -6.77 | -14.7 | -22.7 |  |

| $Uout{FOR f = 95} - Uout{FOR f = 150} = -23.1 - 1.17 = -21.93 Db$ |       |       |       |       |       |       |       |       |       |  |

A Peer-reviewed journal Volume 2, Issue 3, March 2025 DOI 10.17148/IMRJR.2025.020311

The frequency response of the designed digital BPF is shown in figure (11).

Fig. (11): The frequency response of the designed digital BPF

From the figures we notice that the designed BPF works correctly (passes the signal of frequencies 100,150,200 KHz, and suppresses the signal of frequencies 95, 97, 203,205 KHz).

#### VIII. DISCUSSION AND CONCLUSIONS

- -Using digital filtering techniques in communication domain allows implementing different filters (LPF, HPF, BPF, SBF etc) with high accuracy and speed, and with the ability of changing parameters of signals in wide range.

- -Using DDFS techniques in communication domain allows implementing the digital processing in the communication receiver on high intermediate frequency.

- -We note from the practical results the big identification-similarity between the theoretical results and the practical results, which indicates the high accuracy of digital filtering for signals.

- -The designs can be developed and modified according to user requirements due to the use of reprogrammable chips (FPGA).

- -The most important thing in this paper is the possibility of changing the frequency of the input signals.

- -The performance or specifications of a digital filter can be improved by:

- Increasing the filter order.

- Increasing the number of bits of the input signal.

- Changing the window type.

#### REFERENCES

- [1] Volnei A. Pedroni, "Circuit Design With VHDL", MIT Press Cambridge, Massa- chusetts London, England (2004) 364.

- [2] Emmanuel S. Kolawole, Warsame H. Ali, Penrose Cofie, John Fuller, C. Tolliver, Pamela Obiomon "Design and Implementation of Low-Pass, High-Pass and Band-Pass Finite Impulse Response (FIR) Filters Using FPGA ", Circuits and Systems, 2015, 6, 30-48 Published Online February 2015 in SciRes. http://www.scirp.org/journal/cshttp://dx.doi.org/10.4236/cs.2015.62004.

- [3] ALTERA, CORPORATION," Cyclone II Device Family Data Sheet"; 2005.

- [4] Dr. Kamal Aboutabikh, Dr. Abdul-Aziz Shokyfeh, Dr. Amer Garib, "Design and Implementation of a Digital Quadrature Amplitude Modulator QAM-16 using FPGA", International Multidisciplinary Research Journal Reviews, Volume 1, Issue, 2, October 2024.

- [5] Steve Winder, Analog and Digital Filter Design, second edition, Elsevier Science, USA (2002) 450.

- [6] Manoj Sharma, Hemant Dalal, "Designing and implementation of digital filter for power line interference suppression", Int.J.Sci.Eng. Technol.Res.3(6) (2014)1831–1836, June.

- [7] (http://www.mathworks.com/matlabcentral/fileexchange/10858-ecg-simulation-using-matlab).

- [8] GOLDBERG B. "Digital Frequency Synthesis Demystified", LLH Technology Publishing, united states, 334,1999-.

- [9] ANALOG DIVISE, "A Technical Tutorial on Digital Signal Synthesis".

A Peer-reviewed journal Volume 2, Issue 3, March 2025 DOI 10.17148/IMRJR.2025.020311

#### **BIOGRAPHY**

**Dr. Kamal Aboutabikh:** Holds a PhD in communication engineering in 1988 from the USSR, university of communication in Leningrad. Holds assistant professor degree in 2009 from Aleppo university.

Lecturer at Department of Biomedical Engineering, Al Andalus University For Medical Sciences-Syria. Lecturer at Tishreen University-Syria , and Corduba Private University-Syria. Former Lecturer at Kassala University-Sudan and Ittihad Private University-Syria. Published a lot of researches in the field of digital communication, and digital signal processing in the university's journals of Syria and in the European and Indian journals. Working in the field of programming FPGA by using VHDL, and designing Digital Filters.

**Dr. Maarouf Yousef**: Holds a PhD in electrical engineering in 2001 from the Egypt, technical engineering faculty. Holds assistant professor degree in 2009 from Aleppo university. Lecturer at electronic engineering faculty, Al Assad academy, Aleppo University -Syria. Published a lot of researches in the field of digital signal processing, radar signal processing, GPS system. in the university's journals of Syria. Working in the fields of digital circuit design, and programming FPGA by using VHDL, digital signal processing.