# Design and Implementation of a Digital Amplitude Demodulator using FPGA

# Dr. Kamal Aboutabikh

Faculty of Informatics Engineering, Ittihad Private University, Damascus- Syria

**Abstract:** In this paper, we propose the design and implementation mechanism for a digital amplitude demodulator based on the use of Direct Digital Frequency Synthesizer (DDFS) and digital filter using Cyclone II EP2C20F484C7 FPGA from ALTERA placed on education and development board DE-1. The proposed demodulator has the following parameters:

-Clock frequency: F<sub>CLK</sub>=50MHz.

-Sampling frequency:  $f_{sam} = 40 \text{ KHz}$ : ( $f_{sam} = F_{CLK}/K = 50000 \text{ KHz}/1250 = 40 \text{ KHz}$ ).

-Cut- off frequency of the low pass filter (LPF): fcut=2 KHz

-Modulation type of signal is: AM, LSB with carrier, USB with carrier.

-The modulating signal is sinusoidal of frequency: fmod=1 KHz, fmod=1.5 KHz (fmod<= fcut).

-Carrier type: is sinusoidal with frequency: fcar=10 KHz.

-The ROM capacity for the stored signal samples 8192X8 bits, and their values are positive within the range from 0 to 255.

-Frequency range: (3 Hz...25 MHz).

-Frequency Resolution: (3 Hz).

-Signal amplitude (5V).

-Digital designs allow the slides to modify and design development for results and better!!! through reprogramming, depending on the user's desire.

Keywords: digital amplitude demodulator ,USB , LSB , DDFS , FPGA.

### I. INTRODUCTION

1- The single side band (SSB) signal for upper side band (USB) is given according to the following mathematical relation [1]:

$$V(t)_{usb} = \frac{mV_{car}}{2}cos(w_{car} + w_{mod})t$$

(1)

Where:

m: index modulation (m=0,...,1) , w<sub>car</sub>= $2\pi f_{car}$ , w<sub>mod</sub>= $2\pi f_{mod}$ , V<sub>car</sub> carrier amplitude. The carrier signal is given according to the following mathematical relation:

$$V(t)_{car} = V_{car} cos w_{car} t \tag{2}$$

The signal of the product carrier and upper side band is given according to the following mathematical relation:

$$V(t)_{usb} V(t)_{car} = \left\{ \frac{mV_{car}}{2} \cos(w_{car} + w_{mod})t \right\} * \left\{ V_{car} \cos w_{car}t \right\}$$

(3)

$$V(t)_{usb} V(t)_{car} = \frac{m V_{car}^{2}}{2} \cos(w_{car} + w_{mod})t * \cos w_{car}t$$

(4)

$$V(t)_{usb} V(t)_{car} = \frac{m V_{car}^{2}}{4} \{ \cos(2w_{car} + w_{mod})t + \cos w_{mod}t \}$$

(5)

Using the digital LPF with a cut-off frequency (fcut), the following signal can be removed:

$$\frac{m.V_{car}^{2}}{4} \{ \cos(2w_{car} + w_{mod})t \}$$

(6)

The output signal of the digital low pass filter (LPF):

$$V(t)_{dem} = \frac{m V_{car}^2}{4} cosw_{mod} t$$

<sup>(7)</sup>

2- The single side band (SSB) signal for lower side band (LSB) is given according to the following mathematical relation:

$$V(t)_{lsb} = \frac{mV_{car}}{2}cos(w_{car} - w_{mod})t$$

(8)

The carrier signal is given according to the following mathematical relation:

$$V(t)_{car} = V_{car} cos w_{car} t$$

The signal of the product carrier and lower side band is given according to the following mathematical relation :

$$V(t)_{lsb} V(t)_{car} = \left\{ \frac{mV_{car}}{2} \cos(w_{car} - w_{mod})t \right\} * \{V_{car} \cos w_{car}t\}$$

(9)

$$V(t)_{lsb} V(t)_{car} = \frac{m V_{car}^{2}}{2} \cos(w_{car} - w_{mod}) t * \cos w_{car} t$$

(10)

$$V(t)_{lsb} V(t)_{car} = \frac{m V_{car}^{2}}{4} \{ \cos(2w_{car} - w_{mod})t + \cos w_{mod}t \}$$

(11)

Using the digital LPF with a cut- off frequency (fcut), the following signal can be removed:

$$\frac{m.V_{car}^{2}}{4} \{ \cos(2w_{car} - w_{mod})t \}$$

(12)

The output signal of the digital low pass filter (LPF):

$$V(t)_{dem} = \frac{m V_{car}^2}{4} cosw_{mod} t$$

<sup>(13)</sup>

3- The AM signal (carrier and USB and LSB) is given according to the following mathematical relation:

$$V(t)_{AM} = V_{car} \cos w_{car} t + \frac{mV_{car}}{2} \cos(w_{car} + w_{mod})t + \frac{mV_{car}}{2} \cos(w_{car} - w_{mod})t$$

(14)

The carrier signal is given according to the following mathematical relation :

$$V(t)_{car} = V_{car} cos w_{car} t$$

The signal of the product carrier and AM signal is given according to the following mathematical relation :

$$V(t)_{AM} V(t)_{car} = \left\{ V_{car} \cos w_{car} t + \frac{mV_{car}}{2} \cos(w_{car} + w_{mod})t + \frac{mV_{car}}{2} \cos(w_{car} - w_{mod})t \right\} \\ * \left\{ V_{car} \cos w_{car} t \right\}$$

(15)

$$V(t)_{AM} V(t)_{car} = V_{car}^{2} \cos^{2} w_{car} t + \frac{m V_{car}^{2}}{4} \{ \cos(2w_{car} + w_{mod})t + \cos w_{mod} t \} + \frac{m V_{car}^{2}}{4} \{ \cos(2w_{car} - w_{mod})t + \cos w_{mod} t \}$$

(16)

Using the digital LPF with a cut off frequency (fcut), the following two signals can be eliminated

$$\frac{m.V_{car}^{2}}{4} \{ \cos(2w_{car} + w_{mod})t \} + \frac{m.V_{car}^{2}}{4} \{ \cos(2w_{car} - w_{mod})t \}$$

(17)

Copyright to IMRJR

imrjr.com

A Peer-reviewed journal Volume 2, Issue 2, February 2025 DOI 10.17148/IMRJR.2025.020204

The output signal of the digital low pass filter (LPF) :

$$V(t)_{dem} = \frac{m \cdot V_{car}^2}{2} cosw_{mod} t$$

(18)

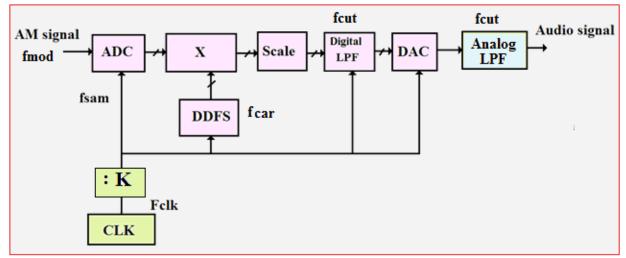

The block diagram of the digital amplitude demodulator using DDFS and digital filter is shown in the figure (1).

Fig. 1: The block diagram of the digital amplitude demodulator using the DDFS and a digital filter

Reference [2] presents the simple method of design and implementation of a digital amplitude demodulator where the order of the FIR filter order is low which makes the filter frequency response function of lower specification.

## **II. RESERCH IMPORTANCE AND ITS OBJECTIVES**

-In this paper, a digital amplitude demodulator was designed, implemented and tested based on the use of Digital Direct Frequency Synthesizer (DDFS) using FPGA, VHDL and Graphical programming language with Quartus II 9.1 design environment.

-Using the digital DDFS with mathematical operations (adding, multiply, division, filtering), makes the digital demodulation design process flexible, accurate and highly efficient.

-Changing the parameters of modulating signal (frequency and amplitude), carrier frequency explains the difference between digital demodulation and analog demodulation.

## **III. RESERCH MATERIALS AND ITS WAYS**

To design, and test the digital demodulator for different modulation types of signals, the following tools and software are used:

-Cyclone II EP2C20F484C7 FPGA chip from ALTERA with highly accuracy, speed, and level specifications, placed on education and development board DE-1 [3].

-DDFS which is considered as highly accuracy techniques in sinusoidal and square signals synthesizing on FPGA chips.

-VHDL programming language with Quartus II 9.1 design environment [4].

-Design Environment MATLAB R2008a

-GDS-1052 digital oscilloscope with Free Wave program to take the results.

-PC computer for designing and injecting the design in the FPGA chip.

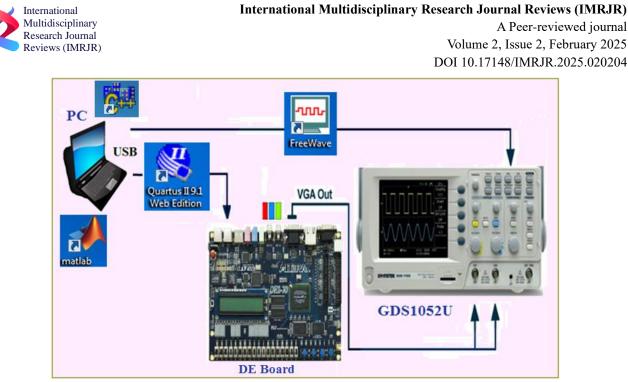

The block diagram of the laboratory experiment platform [5] is shown in figure (2).

Fig (2): Block diagram of the laboratory experiment platform

# IV. THE DESIGN STAGES OF THE DIGITAL AMPLITUDE DEMODULATOR WITH USB USING THE DDFS

1-Convert the analog AM signal to digital signal using ADC for carrier, LSB, USB and AM signals, where : fsam>=2 (fcar+ fmod) For samples of USB signal :

$$V_{AM}(T_{sam}.n) = \frac{mV_c}{2} \cos \frac{2\pi . n(f_c + f_m)}{f_{sam}}$$

(19)

2-Formation the samples of a carrier signal using DDFS according to the mathematical relationship.

$$V_{car}(T_{sam}.n) = V_{car}\cos\left(2\pi f_{car}n T_{sam}\right) = V_{car}\cos\frac{2\pi f_{car}n}{f_{sam}}$$

(20)

3-Formation of the product signal between samples of USB signal and carrier signal samples using DDFS.  $V_{AM}(T_{sam}.n).V_{car}(T_{sam}.n) =$

$$= \left\{ \frac{mV_{car}}{2} \cos \frac{2\pi . n(f_{car} + f_{mod})}{f_{sam}} \right\} \cdot \left\{ V_{car} \cos \frac{2\pi f_{car} n}{f_{sam}} \right\}$$

(21)

$$V_{AM}(T_{sam}.n).V_{car}(T_{sam}.n) = \frac{m V_{car}^{2}}{4} cos\{2\pi (2f_{car} + f_{mod})n.T_{sam}\} + \frac{m V_{car}^{2}}{4} cos(2\pi .f_{mod}.n.T_{sam})$$

The following component are removed using a digital low pass filter (LPF):

$$\frac{m V_{car}^{2}}{4} cos\{2\pi (2f_{car} + f_{mod})n.T_{sam}\}$$

(22)

The output signal of the low pass filter (LPF):

$$V(n)_{dem} = \frac{m V_{car}^{2}}{4} \cos(2\pi . f_{mod} . n. T_{sam})$$

(23)

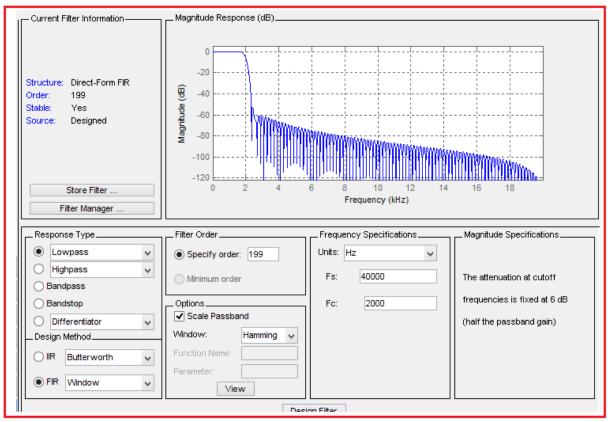

4- Design the digital low pass filter (LPF) using MATLB and VHDL with the following parameters : -Type of filter : LPF .

- Filter structure : Direct form - FIR

-Filter order : 199.

-Filter length : 200.

-Sampling frequency : 40 KHz.

#### imrjr.com

-Frequency of modulating signal : 1 KHz.

-Cut-off frequency of LPF: 2 KHz.

-Window type : Hamming.

-Word length : 8 bits.

The specifications and the magnitude response of a digital filter designed in MATLAB [6] are shown in figure (3).

Fig (3): The specifications and the magnitude response of a digital filter designed in MATLAB

# V. DESIGN OF THE DIGITAL AMPLITUDE DEMODULATOR USIGN DDFS IN QUARTUS II 9.1

We have a DDFS which has the following parameters:

-The frequency step is :  $\delta f = 3 Hz$  ,  $F_{CLK} = 50 MHz$  .

-The modulating signal (MOD) is sinusoidal of frequency fmod=1 KHz and frequency of carrier signal fcar=10KHz. -Modulation type: AM, USB, LSB.

-The ROM capacity for the stored signal samples 8192X8 bits and their values are positive within the range from 0 to 255.

-The number of the accumulator bits is computed from the following mathematical relation [7]:

$$\delta f = \frac{F_{CLK}}{2^n}$$

$$\delta f = \frac{F_{CLK}}{2^n} \Longrightarrow 2^n = \frac{F_{CLK}}{\delta f} = \frac{50 \times 10^6}{3} = 24 \text{ bits}$$

(24)

-The frequency range for the carrier and modulating signals synthesizer is computed from the following mathematical relation [8]:

$$\Delta f = 0 \dots \frac{F_{CLK}}{2} = 0 \dots 25 MHz$$

-To synthesize two signals of frequencies  $f_{car} = 10 \text{ KHz}$ ,  $f_{mod} = 1 \text{ KHz}$ , the frequency code must be [8]:

$$Code F = L = \frac{F \cdot 2^{n}}{F_{CLK}}$$

(25)

International Multidisciplinary Research Journal Reviews (IMRJR)

A Peer-reviewed journal Volume 2, Issue 2, February 2025 DOI 10.17148/IMRJR.2025.020204

Code

$$f_{car} = L_{car} = \frac{f_{car} \cdot 2^{n}}{F_{CLK}} = \frac{0.01 \times 2^{24}}{50} = 3355$$

Code  $f_{mod} = L_{mod} = \frac{f_{mod} \cdot 2^{n}}{F_{CLK}} = \frac{0.001 \times 2^{24}}{50} = 355$

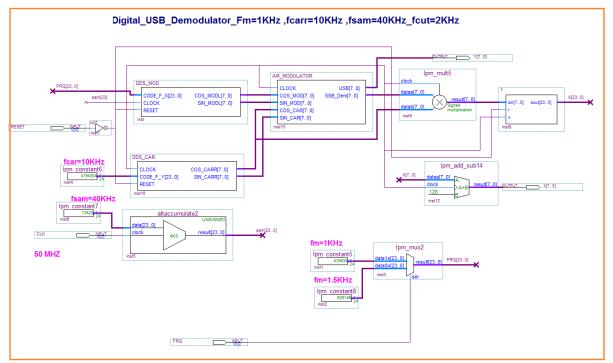

The block diagram of a digital amplitude (USB ) demodulator is shown in figure (4) [8].

Fig (4) : The block diagram of a digital amplitude (USB) demodulator

## VI. RESULTS OF DESIGN

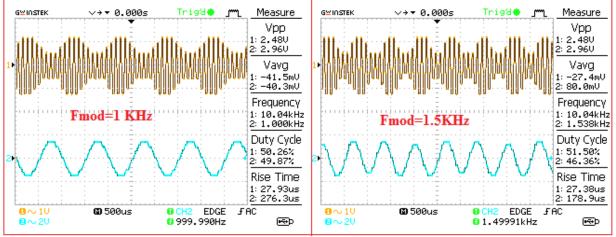

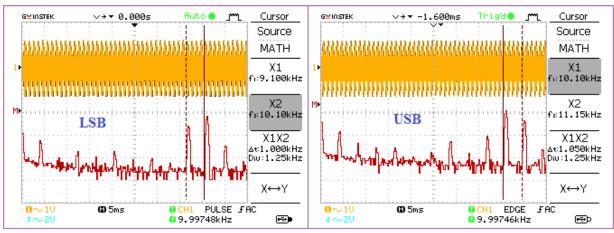

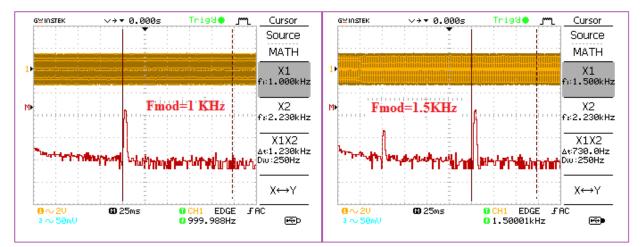

The results of the practical design for the digital amplitude demodulator for different cases (LSB with carrier and USB with carrier) for fmod=1 KHz , fmod=1.5 KHz and fcar =10KHz in time domain according to the previous application using the FPGA chip placed on education and development board DE1 are shown in figure. (5). The results of the practical design for the digital amplitude demodulator for different cases (USB, LSB) in frequency domain according to the previous application using the FPGA chip placed on education and development board DE1 are shown in figure (6) and figure (7). these figures are taken from the screen of digital oscilloscope, and digital spectrum analyzer. We can notice the identification between the theoretical results and the practical results, which indicate the high accuracy of digital synthesizing and modulation operations for these signals. There is a need to refer that the compressing algorithms to a half are used for DDS\_MOD, DDS\_CAR because of using four DDFS and this requires four ROM memories, these memories exist on the FPGA chip placed on education and development board DE1 of capacity 239616 bits (30 KB).

Fig. 5: The AM signal for fmod=1KHz and fmod =1.5KHz in time domain.

Fig. 6: The AM signal for fmod =1KHz, LSB with carrier and USB with carrier in frequency domain

Fig. 7: The modulating signal at the output of digital amplitude demodulator for fmod =1 KHz , and fmod =1.5KHz in frequency domain

## VII. DISCUSSION AND CONCLUSIONS

-The use of high-order of FIR filters makes the digital filtering process of the demodulator accurate and efficient. -The higher order of FIR , the more unwanted frequency components are removed, thus improving the demodulation process.

imrjr.com

A Peer-reviewed journal Volume 2, Issue 2, February 2025 DOI 10.17148/IMRJR.2025.020204

-Using DDFS techniques in communication domain allows implementing different digital modulation and demodulation operations (AM, FM, PM, SSB etc) with high accuracy and speed in digital signal synthesizing, and with the ability of changing parameters in wide range.

-Using DDFS techniques in communication domain allows implementing the digital processing in the communication receiver on high intermediate frequency.

-We notice from the practical results the big identification-similarity between the theoretical results and the practical results, which indicates the high accuracy of digital synthesizing and modulation operations for signals.

-The designs can be developed and modified according to user requirements due to the use of reprogrammable chips (FPGA).

-The most important thing in this paper is the possibility of changing the frequency of the modulation signal, and the frequency of the carrier signal.

## REFERENCES

- [1]. Dr. Kamal Aboutabikh , "Design and Implementation of a Digital Single Side Band (SSB) Modulator using FPGA", International Multidisciplinary Research Journal Reviews (IMRJR) A Peer-reviewed journal Volume 2, Issue 2, February 2025.

- [2]. Predrag Jovanović, Department of Radio communications IRITEL A.D. Belgrade, Serbia, Dejan Rakić, Bogdan Marković, Department of Digital communication BITGEAR WIRELESS DESIGN SERVICES D.O.O. Belgrade, Serbia, FPGA Implementation of Demodulators in Software Defined Radio Systems, INFOTEH-JAHORINA Vol. 12, March 2013.

- [3]. ALTERA, CORPORATION," Cyclone II Device Family Data Sheet"; 2005.

- [4]. Volnei A. Pedroni, "Circuit Design With VHDL", MIT Press Cambridge, Massa- chusetts London, England (2004) 364.

- [5]. Dr. Kamal Aboutabikh, Dr. Abdul-Aziz Shokyfeh, Dr. Amer Garib, "Design and Implementation of a Digital Quadrature Amplitude Modulator QAM-16 using FPGA", International Multidisciplinary Research Journal Reviews, Volume 1, Issue, 2, October 2024.

- [6]. MATLAB / SIMULINK , MathWorks , 2011.

- [7]. GOLDBERG B. 1999- "Digital Frequency Synthesis Demystified", LLH Technology Publishing, united states, 334.

- [8]. "ANALOG DIVISES", A Technical Tutorial on Digital Signal Synthesis.

#### BIOGRAPHY

**Dr. Kamal Aboutabikh** holds a PhD in communication engineering in 1988 from the USSR , university of communication in Leningrad , holds a degree assistant professor in 2009 from Aleppo university.

Lecturer at Department of Biomedical Engineering, Al Andalus University For Medical Sciences-Syria ,Tishreen University-Syria ,Corduba Private University-Syria , Kassala University-Sudan and Ittihad Private University- Syria.

Published a lot of researches in the field of digital communication and digital signal processing in the universities journals of Syria and in the European and Indian journals.

Working in the field of programming FPGA by using VHDL, and design of Digital Filters.