# Design and Implementation of a Digital Quadrature Amplitude Modulator QAM-32 using FPGA

## Dr. Kamal Aboutabikh<sup>1</sup>, Dr. Abdul-Aziz Shokyfeh<sup>2</sup>, Dr. Amer Garib<sup>3</sup>

Faculty of Informatics Engineering, Ittihad Private University, Damascus- Syria<sup>1,2,3</sup>

aboutabikh59@gmail.com

## Abstract

In this paper, we propose the design and implementation mechanism for different digital modulators such as Quadrature Amplitude QAM-32 modulators based on the use of Quadrature Direct Digital Frequency Synthesizer (QDDFS) using Cyclone II EP2C20F484C7 FPGA from ALTERA placed on education and development board DE-1 with the following parameters:

- Clock frequency :  $F_{CLK}$ =50MHz .

- Modulation type of signal is : QAM-32 .

- Frequency range : (0.011 Hz...10 MHz).

- Frequency Resolution : (0.011 Hz).

- Signal amplitude(5V).

- Data frequency : 1KHz.

- Digital designs allow the slides to modify and design development for results and better through reprogramming, depending on the user's desire.

Keywords: Digital Modulator, QAM, QAM-32, DDFS, QDDFS, FPGA.

I =

#### I. Introduction

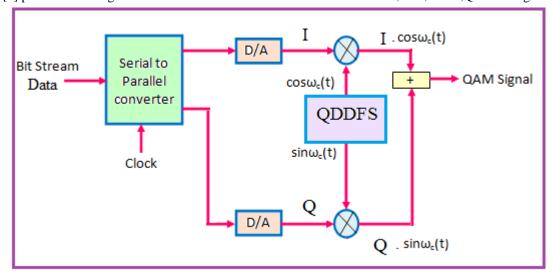

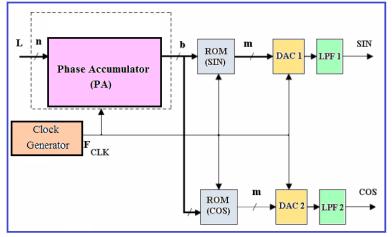

The mathematical principle of digital QAM modulation using QDDFS can be explained according to the diagram [1] shown in figure (1), where the Quadrature Amplitude Modulation achieved on multiply of data signal and samples of sinusoidal and cosine signals [2] stored in ROMs of QDDFS.

QAM-32 modulation achieved on adding (I.  $\cos w_c t$ ) and (Q.  $\sin w_c t$ ) signals from the QDDFS , where:

$$\pm 1$$

,  $\pm 3$ ,  $\pm 5$ ,  $\pm 7$ ,  $Q = \pm 1$ ,  $\pm 3$  (1)

The stored values of the sine and cosine signals in ROM of DDFS and QDDFS are calculated according to the following equation [3]:

$$U_{SIN}(i) = INT \left[ \left( 2^{m-1} - 1 \right) \cdot \sin \left( \frac{360 \cdot i}{2^{b}} \right) \right]$$

(2)

$$U_{COS}(i) = INT \left[ \left( 2^{m-1} - 1 \right) \cdot \cos \left( \frac{360 \cdot i}{2^{b}} \right) \right]$$

For:

m = 8 bits, b = 13 bits,

$$i = (0...2^{b} - 1) = (0...8191)$$

Then:

A Peer-reviewed journal Volume 1, Issue 2, October 2024 DOI 10.17148/IMRJR.2024.010204

$$U_{SIN}(i) = INT \left[ \left( 2^{8-1} - 1 \right) \cdot \sin \left( \frac{360.i}{2^{13}} \right) \right] = INT \left[ 127.\sin \left( \frac{360.i}{8192} \right) \right]$$

$$U_{cos}(i) = INT \left[ \left( 2^{8-1} - 1 \right) \cdot \cos \left( \frac{360.i}{2^{13}} \right) \right] = INT \left[ 127.\cos \left( \frac{360.i}{8192} \right) \right]$$

$$U_{sin}(i) = (-127.....+127)$$

$$U_{cos}(i) = (-127.....+127)$$

To avoid negative values that are difficult to store in memory, we add a value off-set= 128

$$U_{sin}(i) = (0....255)$$

$U_{cos}(i) = (0....255)$

In paper [4] present the design and simulation only of a modulation module for ASK using VHDL. In paper [5] present the design and simulation of a modulation module for ASK, FSK, BPSK, QPSK using VHDL.

Figure (1) Block diagram of digital QAM modulator using QDDFS

## II. Research importance and its objectives

-In this paper digital QAM-32 modulator were designed, implemented and tested based on the use of Quadrature Digital Direct Frequency Synthesizer (QDDFS) using FPGA, VHDL and Graphical programming language with Quartus II 9.1 design environment.

-Using the digital QDDFS with mathematical operations (adding, multiply, division), makes the digital modulation design process flexible, accurate and highly efficient.

-Changing the data signal frequency, carrier signal frequency, frequency deviation and phase shift within different values explains the difference between digital modulation and analog modulation .

#### III. Research materials and its ways

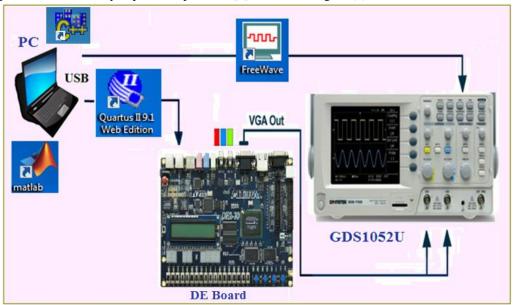

To design, and test the digital modulators for different modulation types of signals, the following tools and software are used:

-Cyclone II EP2C20F484C7 FPGA chip from ALTERA with highly accuracy, speed, and level specifications, placed on education and development board DE-1 [6].

-DDFS which is considered as highly accuracy techniques in sinusoidal and square signals synthesizing on FPGA chips.

-VHDL programming language with Quartus II 9.1 design environment [7].

-Design Environment MATLAB R2008a

-GDS-1052 digital oscilloscope with Free Wave program to take the results.

-PC computer for designing and injecting the design in the FPGA chip.

A Peer-reviewed journal Volume 1, Issue 2, October 2024 DOI 10.17148/IMRJR.2024.010204

The block diagram of the laboratory experiment platform [8] is shown in figure (2).

Figure (2) Block diagram of the laboratory experiment platform

| IV.      | Block | and | functional | diagrams  | of a | digital | OAM-32   |

|----------|-------|-----|------------|-----------|------|---------|----------|

| <b>T</b> | DIOCK | anu | runctional | ulagianis | or a | ungnun  | Q1111-54 |

The characteristics of QAM types is shown in table 1:

| Table.1 : types of QAM |                       |                    |  |  |  |  |  |  |

|------------------------|-----------------------|--------------------|--|--|--|--|--|--|

| Name of scheme         | Bit per symbol (bits) | Number of symbols  |  |  |  |  |  |  |

| QAM-4                  | 2                     | 2 <sup>2</sup> =4  |  |  |  |  |  |  |

| QAM-8                  | 3                     | 23=8               |  |  |  |  |  |  |

| QAM-16                 | 4                     | 24=16              |  |  |  |  |  |  |

| QAM-32                 | 5                     | 2 <sup>5</sup> =32 |  |  |  |  |  |  |

| QAM-64                 | 6                     | 26=64              |  |  |  |  |  |  |

The QAM-32 signal is given according to the fallowing equation [3] :

$$U_{QAM-32}(t) = I.\cos(2\pi f_c t) + Q.\sin(2\pi f_c t)$$

(3)

$$U_{QAM-32}(t) = A.\sin(2\pi f_c t + \theta)$$

Where:

Amplitude = A =

$$\sqrt{(I)^2 + (Q)^2} = \sqrt{I^2 + Q^2}$$

(4)

Phase =

$$\theta = tan^{-1} \left(\frac{Q}{I}\right)$$

(5)

Where:  $I = \pm 1$ ,  $\pm 3$ ,  $\pm 5$ ,  $\pm 7$ ,  $Q = \pm 1$ ,  $\pm 3$ , (w<sub>c</sub>) carrier frequency of signal.

Values of Data (00000, ....., 11111), I component, Q component, QAM-32 output signal ,amplitude and phase QAM-32 given according to the table .2, the constellation diagrams of QAM-32 signal shown in figure (3).

| Table .2 values of : I, Q, QAM-32, Phase and Amplitude QAM-32 |       |    |    |        |        |              |       |           |              |

|---------------------------------------------------------------|-------|----|----|--------|--------|--------------|-------|-----------|--------------|

| Ν                                                             | Data  | Ι  | Q  | I*cos  | Q*sin  | Out          | Phase | Amplitude | Scale factor |

| 0                                                             | 00000 | -7 | -3 | -7 cos | -3 sin | -7 cos-3sin  | 203   | 7.6       | 8            |

| 1                                                             | 00001 | -7 | -1 | -7 cos | - sin  | -7 cos - sin | 188   | 7.1       | 8            |

A Peer-reviewed journal

Volume 1, Issue 2, October 2024 DOI 10.17148/IMRJR.2024.010204

|    | DOI 10.17148/IMRJR.2024.010 |    |    |         |          |              |     |     |   |  |

|----|-----------------------------|----|----|---------|----------|--------------|-----|-----|---|--|

| 2  | 00010                       | -7 | 3  | -7 cos  | 3 sin    | -7 cos+3sin  | 157 | 7.6 | 8 |  |

| 3  | 00011                       | -7 | +1 | -7 cos  | $+ \sin$ | -7 cos+sin   | 172 | 7.1 | 8 |  |

| 4  | 00100                       | -5 | -3 | -5 cos  | -3 sin   | -5 cos- 3sin | 211 | 5.8 | 6 |  |

| 5  | 00101                       | -5 | -1 | -5 cos  | - sin    | -5 cos- sin  | 192 | 5.1 | 6 |  |

| 6  | 00110                       | -5 | 3  | -5 cos  | 3 sin    | -5 cos+3 sin | 149 | 5.8 | 6 |  |

| 7  | 00111                       | -5 | 1  | -5 cos  | $+\sin$  | -5 cos+ sin  | 169 | 5.1 | 6 |  |

| 8  | 01000                       | -1 | -3 | - cos   | -3 sin   | - cos-3sin   | 252 | 3.2 | 4 |  |

| 9  | 01001                       | -1 | -1 | - cos   | - sin    | - cos- sin   | 225 | 1.4 | 2 |  |

| 10 | 01010                       | -1 | +3 | - cos   | +3 sin   | - cos+ 3sin  | 109 | 3.2 | 4 |  |

| 11 | 01011                       | -1 | 1  | - cos   | $+\sin$  | - cos+ sin   | 135 | 1.4 | 2 |  |

| 12 | 01100                       | -3 | -3 | -3 cos  | -3 sin   | -3 cos-3sin  | 225 | 4.2 | 5 |  |

| 13 | 01101                       | -3 | -1 | -3cos   | - sin    | -3cos- sin   | 199 | 3.2 | 4 |  |

| 14 | 01110                       | -3 | 3  | -3 cos  | +3 sin   | -3 cos+3sin  | 135 | 4.2 | 5 |  |

| 15 | 01111                       | -3 | 1  | -3 cos  | $+\sin$  | -3 cos+sin   | 174 | 3.2 | 4 |  |

| 16 | 10000                       | 7  | -3 | +7 cos  | -3 sin   | +7 cos-3sin  | 337 | 7.6 | 8 |  |

| 17 | 10001                       | 7  | -1 | +7 cos  | - sin    | +7 cos-sin   | 352 | 7.1 | 8 |  |

| 18 | 10010                       | 7  | 3  | +7 cos  | +3 sin   | +7 cos+3sin  | 24  | 7.6 | 8 |  |

| 19 | 10011                       | 7  | 1  | +7 cos  | $+\sin$  | +7 cos+sin   | 9   | 7.1 | 8 |  |

| 20 | 10100                       | 5  | -3 | +5 cos  | -3 sin   | +5 cos-3sin  | 329 | 5.8 | 6 |  |

| 21 | 10101                       | 5  | -1 | +5 cos  | - sin    | +5 cos- sin  | 349 | 5.1 | 6 |  |

| 22 | 10110                       | 5  | 3  | +5 cos  | +3 sin   | +5 cos+3sin  | 31  | 5.8 | 6 |  |

| 23 | 10111                       | 5  | 1  | +5 cos  | $+\sin$  | +5 cos+sin   | 12  | 5.1 | 6 |  |

| 24 | 11000                       | 1  | -3 | $+\cos$ | -3 sin   | + cos-3sin   | 289 | 3.2 | 4 |  |

| 25 | 11001                       | 1  | -1 | cos     | - sin    | +cos-sin     | 315 | 1.4 | 2 |  |

| 26 | 11010                       | 1  | 3  | $+\cos$ | +3 sin   | + cos+3sin   | 72  | 3.2 | 4 |  |

| 27 | 11011                       | 1  | 1  | $+\cos$ | $+\sin$  | + cos+sin    | 45  | 1.4 | 2 |  |

| 28 | 11100                       | 3  | -3 | +3 cos  | -3 sin   | +3 cos_3sin  | 315 | 4.2 | 5 |  |

| 29 | 11101                       | 3  | -1 | +3 cos  | - sin    | +3 cos-sin   | 342 | 3.2 | 4 |  |

| 30 | 11110                       | 3  | 3  | 3 cos   | +3sin    | +3 cos+3sin  | 45  | 4.2 | 5 |  |

| 31 | 11111                       | 3  | 1  | +3 cos  | $+\sin$  | +3 cos+sin   | 19  | 3.2 | 4 |  |

|    |                             | •  | -  |         |          |              |     | -   |   |  |

International Multidisciplinary Research Journal Reviews (IMRJR) A Peer-reviewed journal Volume 1, Issue 2, October 2024 IMRIR DOI 10.17148/IMRJR.2024.010204 Q 010,10 3 011.10 000,10 110,10 111,10 001.10 101 .10 100,10 011.11 010.11 110.11 101.11 000.11 001.11 111.11 100.11 I -3 -5 0 3 5 -7 -1 1 7 -1 000,01 001,01 011.01 010,01 110,01 111,01 101,01 100,01 000,00 001,00 011,00 010,00 110,00 .00 101.00 100,00

Figure (3) the constellation diagrams of QAM-32 signal

The signal frequency (f) and frequency code (L) of QDDFS is calculated according to the fallowing equations [3]:

$$f = \frac{L.F_{CLK}}{2^n}$$

(6)

$$L = \frac{f.2^n}{F_{CLK}}$$

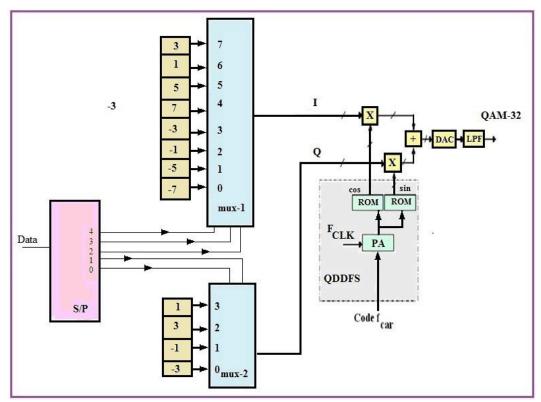

The functional diagram of digital QAM-32 modulator using QDDFS is shown in figure (4), where every (5) bits are represented by a single signal with its own amplitude and phase, and thus the (5) bits have (32) different combinations, where the two LSB bits represent the (Q) component and the three MSB bits represent the (I) component.

Figure (4) Block diagram of digital QAM-32 using QDDFS

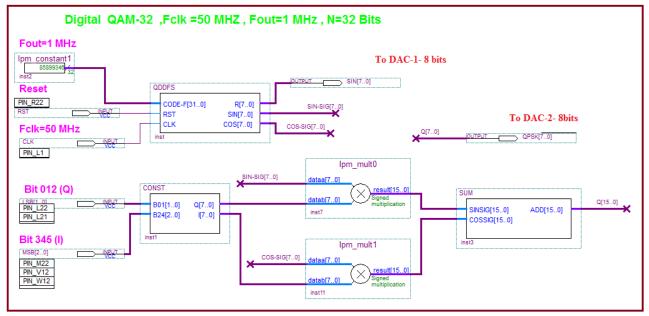

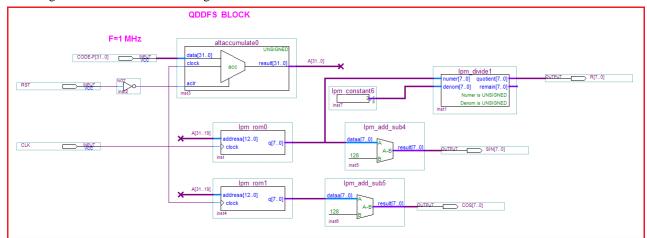

The functional diagram of digital QAM-32 modulator in Quartus II 9.1 design environment is shown in figure (5) where output signals are data signal and QAM-32 signal with the following parameters [9]:

- -Clock frequency: F<sub>CLK</sub>=50 MHz

- -Modulation type of signal is : QAM-32.

- -Carrier frequency of QAM-32 : f= 1 MHz.

- -Frequency of data signal : 1 KHz

- -Frequency range of QDDFS : (0.011 Hz...25 MHz).

- -Frequency Resolution of QDDFS : (0.011 Hz).

- -Size of QDDFS ROM: 2 x 13KB.

- -DAC :with 8 bits.

- -Bits numbers of Phase Accumulator : n=32 bits

- -Signal amplitude (5V).

For

$$f = 1 \text{ MHz} \Rightarrow CODE f = L = \frac{f \cdot 2^n}{F_{CLK}} = \frac{1 \cdot 2^{32}}{50} = 85899346$$

Figure (5) functional diagram of digital QAM-32 in Quartus II 9.1 design environment

#### V. Block and functional diagrams of a QDDFS

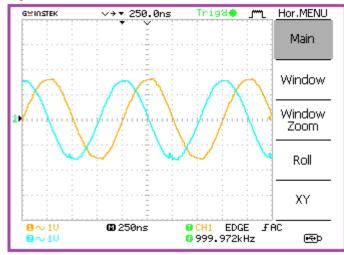

The QDDFS is assigned to form two signals, the first a sine and the second a cosine, with a phase shift of 90 degrees between them at a frequency of 1 MHz.

The block diagram of digital QDDFS is shown in figure (6), it is consists of ROM\_SIN for a sine wave and ROM\_COS for a cosine waves and phase accumulator with 32 bits, LPF1 (low pass filter), LPF2, DAC1, DAC2 and clock generator ( $F_{CLK}$ =50 MHz), where L represents the generated frequency code according to the mathematical relation (5).

A Peer-reviewed journal Volume 1, Issue 2, October 2024 DOI 10.17148/IMRJR.2024.010204

Figure (6) block diagram of QDDFS

The functional diagram of digital QDDFS in Quartus II 9.1 design environment is shown in figure (7), it is consists of a sine wave generator and a cosine wave generator.

Figure (7) functional diagram of QDDFS in Quartus II 9.1 design environment

The result of designed QDDFS in Quartus II 9.1 design environment is shown in figure (8) in time domains , where carrier frequency of signals 1MHz and phase shift is  $90^{\circ}$ .

Figure (8) quadrature signals (sin and cos) in time and

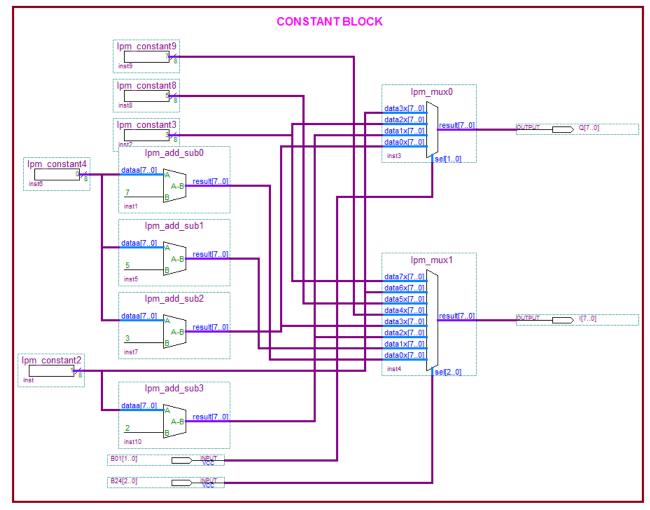

VI. Functional diagrams of a constant block(CONSTANT)

A Peer-reviewed journal

Volume 1, Issue 2, October 2024

DOI 10.17148/IMRJR.2024.010204

The block of constants is assigned to form the constants (7, -7, 5, -5, 3, -3, 1, -1) for the Q component and the (3, -3, 1, -1) for the (I) component.

The functional diagram of Constant block (CONST) in Quartus II 9.1 design environment is shown in figure (9).

Figure (9) functional diagram of constant block in Quartus II 9.1 design environment

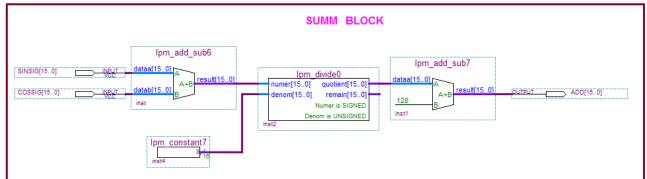

## VII. Functional diagrams of a summation block

The sum block is dedicated to forming the following sum signal:

$$U_{QAM-32}(t) = I.\cos(2\pi f t) + Q.\sin(2\pi f t)$$

$$I = \mp 1$$

,  $\pm 3$ ,  $\pm 5$ ,  $\pm 7$  and  $Q = \mp 1$ ,  $\pm 3$

and also to adjust the scales of the sum signal values so that their digital values are within the limits of the DAC used in the design.

The functional diagram of sum block (CONST) in Quartus II 9.1 design environment is shown in figure (10).

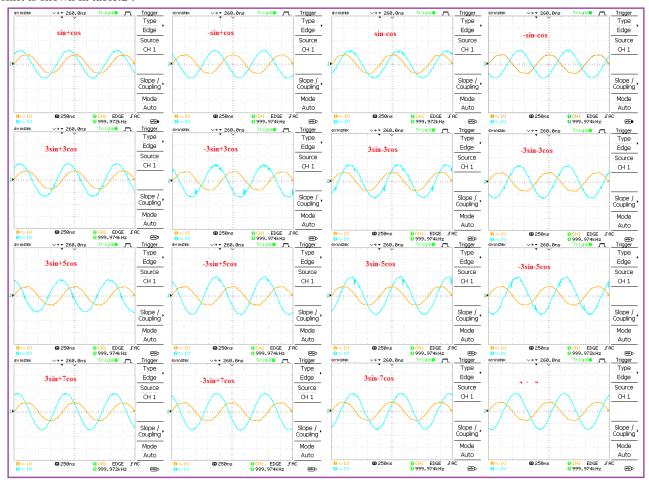

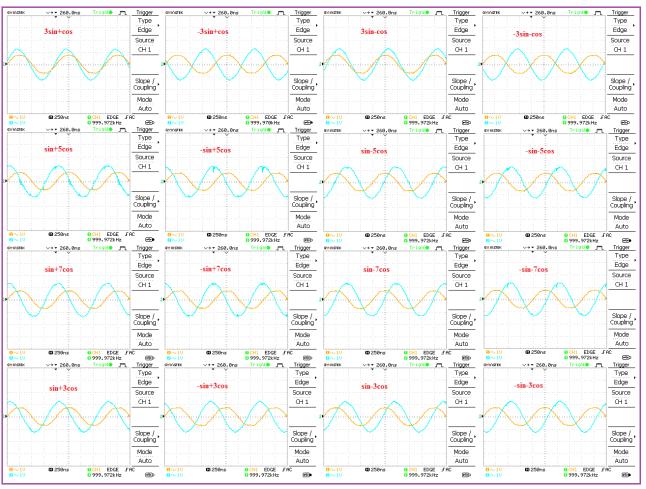

The result of designed digital QAM-32 modulator in Quartus II 9.1 design environment is shown in figure (11-a, b) in time domains , where frequency of data signal : 1 KHz , carrier frequency of QAM-32 : 1 MHz , amplitude and phase shift is shown in table.2 .

Figure (11-a) QAM-32 signals in time domain according values of table.2

A Peer-reviewed journal Volume 1, Issue 2, October 2024 DOI 10.17148/IMRJR.2024.010204

Figure (11-b) QAM-32 signals in time domain according values of table.2

#### VIII. Discussion and Conclusion

-Depending on the previous practical results ,the digital QAM-32 were successfully designed using FPGA.

- In this research, the digital modulators were designed with QDDFS which is considered as a highly accuracy technique in carrier sinusoidal, data signal, and QAM-32 synthesizing on FPGA chips.

- Practical experiments described in the study suggest how these modulators can be used in real communication devices.

- There is a possibility to develop this algorithm through designing digital QAM-64 ,QAM-128,QAM-256 and another modulators types.

#### References

[1] Fuqin Xiong digital Modulation Techniques,-(Artech House telecommunications library) ,/653/ pages., 2000

[2] www.complextereal.com (All About Modulation –Part I)

[3] Goldberg, "Digital Frequency Synthesis Demystified";1999.

[4] Advances in Computer Science Research ,volume 78, 3rd International Workshop on Materials Engineering and Computer Science Research (IWMECS 2018).

[5]MOLABANTI PRAVEEN KUMAR, T.S.R KRISHNA PRASAD, M .VIJAYA KUMA, Implementation of Digital Communication Laboratory on FPGA, International Journal of Advanced Research in Computer and Communication Engineering, Vol. 2, Issue 11, November 2013

[6] ALTERA, CORPORATION," Cyclone II Device Family Data Sheet"; 2005.

[7] ALTERA, CORPORATION," Cyclone II FPGA Starter Development Board";2003.

A Peer-reviewed journal Volume 1, Issue 2, October 2024 DOI 10.17148/IMRJR.2024.010204

[8] Dr. Kamal Aboutabikh, Dr. Ibrahim Haidar, Dr. Amer Garib, Design and Implementation of a Digital FIR LPF with Variable Pass-Band for ECG Signal using FPGA, International Journal of Advanced Research in Computer and Communication Engineering Vol. 4, Issue 9, September 2015.

[9] Volnei A. Pedroni, Circuit Design With VHDL, MIT Press Cambridge, Massa- chusetts London, England (2004) 364.

## BIOGRAPHYs

**Dr. Kamal Aboutabikh** holds a PhD in communication engineering in 1988 from the USSR , university of communication in Leningrad , holds a degree assistant professor in 2009 from Aleppo university. Lecturer at Department of Biomedical Engineering , Al Andalus University For Medical Sciences-Syria ,Tishreen University-Syria ,Corduba Private University-Syria , Kassala University-Sudan and Ittihad Private University- Syria.

Publish a lot of research in the field of digital communication and digital signal processing in the universities journals of Syria and in the European and Indian journals.

Working in the field of programming FPGA by using VHDL and design of Digital Filters.

**Dr. Abdul-Aziz Shokyfeh** holds a PhD in telecom engineering in 2017 from Damascus Syria, Faculty of Mechanical and Electrical Engineering Telecommunication and electronic department . Lecture at Electric engineering , computer engineering , control and automation

engineering, telecom and electronic engineering at Damascus University.

Dean of IT college at Ittehad Private University, from 2023 till now.

Publish a lot of research in field of antenna in Syrian and European journals .Working in field of PBXs,

Network, low current system and solution.

**Dr. Amer Garib** holds a PhD in communication engineering in 1994 from the USSR, university of communication in Leningrad. Lecturer at Department of Faculty of Informatics Engineering , Ittihad Private University- Syria.

Publish a lot of research in the field of digital communication in the universities of Syria and in the Indian journals.

Working in the field of Digital Communication Systems and design of Antenna Systems.